## 适用于 IGBT/SiC、高 CMTI、10A 拉/灌电流的单通道增强隔离栅极驱动器

### 1. 产品特性

- 驱动高达  $2121\text{V}_{\text{PK}}$  的 SiC MOSFET 和 IGBT

- 10A/10A 峰值拉/灌驱动电流能力

- 输入 CMOS 或者 TTL (CA-IS3214TSCG) 逻辑

- 宽电源范围:

- 3.0V 至 5.5V 输入侧 VCC 电源范围

- 高达 33V 的输出驱动电源 (VDD – VEE)，具有两种 UVLO 选项:

- B 版本: 8V

- C 版本: 12.5V

- 输入引脚上 30ns (典型值) 脉冲抑制功能

- 延时特性:

- 80ns (典型值) 传播延迟

- 15ns (最大值) 脉宽失真

- 15ns (最大值) 器件间延时匹配

- SOIC8-WB 封装，爬电距离和电气间隙>8.2mm, 5700V<sub>RMS</sub> 隔离耐压等级

- 高共模瞬态抗扰度: >150kV/ $\mu\text{s}$

- 额定工作电压下隔离栅寿命大于40年

- 工作结温 ( $T_J$ ) 范围: -40°C 至 150°C

- 安全认证 (申请中):

- 根据 DIN EN IEC 60747-17(VDE 0884-17):2021-10 的 VDE 认证

- 根据 UL 1577 的 UL 认证

- 根据 GB4943.1-2022 的 CQC 认证

- 根据 EN 62368-1 和 EN 61010-1 的 TUV 认证

### 2. 典型应用

- 电机逆变器

- 新能源车载充电器

- 光伏逆变器

- 储能变流器

- 充电桩功率模块

- 伺服驱动器

- 变频器

- UPS 及工业电源等

### 3. 概述

CA-IS3214 是一系列基于电容隔离的单通道栅极驱动器，可用于驱动 MOSFET、IGBT、SiC MOSFET 等功率器件。该驱动器具有出色的动态性能和高可靠性，同时具有高达 10A/10A 峰值的拉/灌电流能力。

CA-IS3214 通过  $\text{SiO}_2$  电容隔离技术实现控制侧与驱动侧的电气隔离，支持 1.5kV<sub>RMS</sub> 的隔离工作电压、12.8 kV<sub>PK</sub> 浪涌抗扰度，额定工作电压下隔离栅寿命超过 40 年，同时具有良好的器件一致性以及 >150kV/ $\mu\text{s}$  的共模瞬态抗扰度 (CMTI)。

CA-IS3214 具有控制和驱动侧电源 UVLO 功能，同时针对 SiC 和 IGBT 开关行为进行了优化，并提高了可靠性。此外，CA-IS3214MxG 内置 5A 峰值电流有源米勒钳位；CA-IS3214SxG 和 CA-IS3214TSCG 具有 OUTH 和 OUTL 分离输出配置。

CA-IS3214 输入 IN+/IN- 提供 CMOS 或者 TTL 逻辑选项，其中 CA-IS3214TSCG 为 TTL 逻辑，其它料号为 CMOS 逻辑。

CA-IS3214 器件采用 8 引脚宽体 SOIC 封装。所有器件的额定工作结温范围为 -40°C 至 +150°C。

### 器件信息

| 器件型号          | 封装           | 封装尺寸 (标称值)      |

|---------------|--------------|-----------------|

| CA-IS3214xxG  | SOIC8-WB (G) | 5.85mm x 7.50mm |

| CA-IS3214TSCG |              |                 |

## 简要框图

## 4. 订购指南

表 4-1 有效订购零件编号

| 型号            | IN+/IN-输入逻辑 | 驱动侧 UVLO | OUTPUT 类型 | Miller Clamp | 封装           |

|---------------|-------------|----------|-----------|--------------|--------------|

| CA-IS3214MBG  | CMOS        | 8V       | Single    | 5A           | SOIC8-WB (G) |

| CA-IS3214MCG  | CMOS        | 12.5V    | Single    | 5A           | SOIC8-WB (G) |

| CA-IS3214SBG  | CMOS        | 8V       | Split     | -            | SOIC8-WB (G) |

| CA-IS3214SCG  | CMOS        | 12.5V    | Split     | -            | SOIC8-WB (G) |

| CA-IS3214TSCG | TTL         | 12.5V    | Split     | -            | SOIC8-WB (G) |

# 目录

|                              |           |

|------------------------------|-----------|

| <b>1. 产品特性</b>               | <b>1</b>  |

| <b>2. 典型应用</b>               | <b>1</b>  |

| <b>3. 概述</b>                 | <b>1</b>  |

| <b>4. 订购指南</b>               | <b>2</b>  |

| <b>5. 引脚功能描述</b>             | <b>4</b>  |

| 5.1. CA-IS3214MxG 引脚功能描述     | 4         |

| 5.2. CA-IS3214(T)SxG 引脚功能描述  | 5         |

| <b>6. 产品规格</b>               | <b>6</b>  |

| 6.1. 绝对最大额定值 <sup>1</sup>    | 6         |

| 6.2. ESD 额定值                 | 6         |

| 6.3. 推荐工作条件                  | 6         |

| 6.4. 热量信息                    | 6         |

| 6.5. 隔离特性                    | 7         |

| 6.6. 安全相关认证                  | 8         |

| 6.7. 额定功率                    | 8         |

| 6.8. 安全限值                    | 8         |

| 6.9. 电气特性                    | 9         |

| 6.10. 开关特性                   | 10        |

| 6.11. 典型特性                   | 11        |

| <b>7. 参数测量信息</b>             | <b>13</b> |

| 7.1. 传播延迟                    | 13        |

| 7.2. 输入抗脉冲尖峰滤波器              | 14        |

| 7.3. 有源米勒钳位 (CA-IS3214Mxx)   | 14        |

| 7.4. 欠压锁定 (UVLO)             | 14        |

| 7.4.1. VCC UVLO              | 14        |

| 7.4.2. VDD UVLO              | 15        |

| 7.5. CMTI 测试                 | 15        |

| <b>8. 详细说明</b>               | <b>17</b> |

| 8.1. 概述                      | 17        |

| 8.2. 功能框图                    | 17        |

| 8.3. 特性描述                    | 18        |

| 8.4. 驱动级                     | 18        |

| 8.5. 保护功能                    | 19        |

| 8.5.1. VCC 和 VDD 欠压锁定 (UVLO) | 19        |

| 8.5.2. 主动下拉                  | 19        |

| 8.5.3. 短路钳位                  | 19        |

| 8.5.4. 有源米勒钳位 (CA-IS3214MxG) | 20        |

| 8.5.5. 直通死区保护功能 (STP)        | 20        |

| 8.6. 器件功能模式                  | 22        |

| <b>9. 应用信息</b>               | <b>23</b> |

| 9.1. 典型应用                    | 23        |

| 9.2. 电源设计                    | 23        |

| 9.3. 输入滤波器                   | 23        |

| 9.4. PWM 内部互锁 IN+ 和 IN-      | 24        |

| 9.5. 栅极驱动电阻设计                | 24        |

| 9.6. PCB 设计建议                | 25        |

| 9.6.1. 电源去耦                  | 25        |

| 9.6.2. PCB 布局指南              | 25        |

| <b>10. 封装信息</b>              | <b>26</b> |

| 10.1. SOIC8-WB 封装尺寸          | 26        |

| <b>11. 焊接信息</b>              | <b>27</b> |

| <b>12. 编带信息</b>              | <b>28</b> |

| <b>13. 修订历史</b>              | <b>29</b> |

| <b>14. 重要声明</b>              | <b>30</b> |

## 5. 引脚功能描述

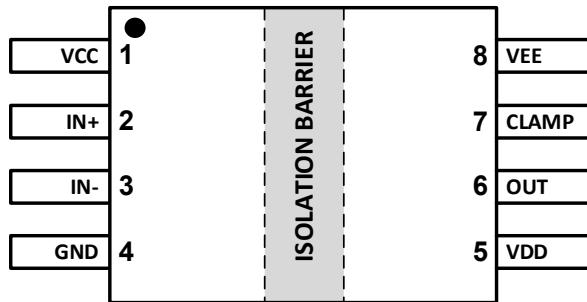

### 5.1. CA-IS3214MxG 引脚功能描述

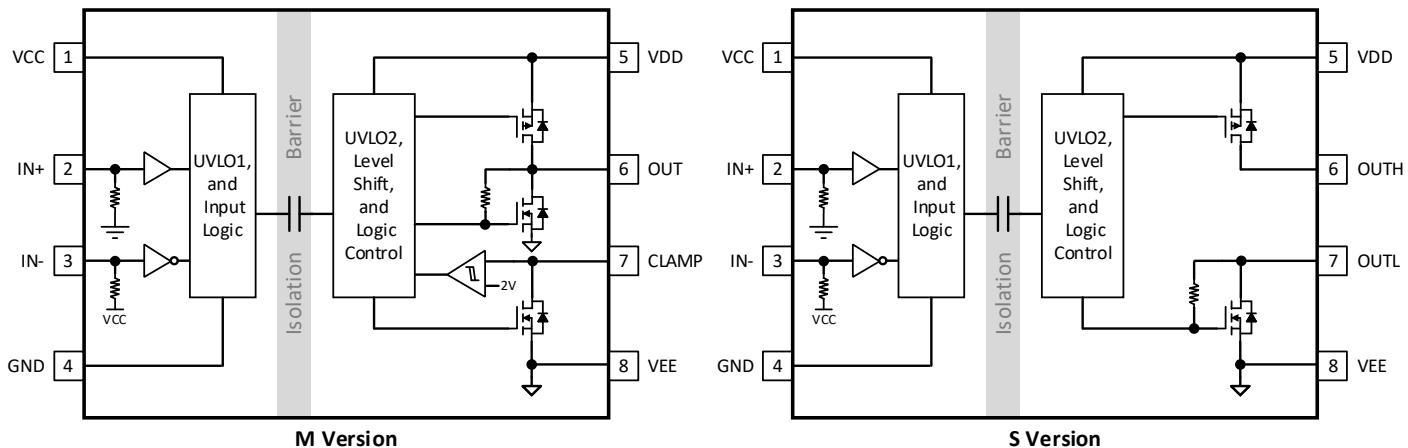

图 5-1 CA-IS3214MxG 引脚配置

表 5-1 引脚功能描述

| 引脚名称  | 引脚编号 | 类型 <sup>1</sup> | 描述                                               |

|-------|------|-----------------|--------------------------------------------------|

| VCC   | 1    | P               | 3V 到 5.5V 的控制侧电源，推荐 1μF 的旁路电容到 GND。              |

| IN+   | 2    | I               | 同相栅极驱动控制输入，内部下拉。                                 |

| IN-   | 3    | I               | 反相栅极驱动控制输入，内部上拉。                                 |

| GND   | 4    | G               | 控制侧的输入电源和逻辑地参考。                                  |

| VDD   | 5    | P               | 栅极驱动电压的正电源，推荐 10μF 的旁路电容到 VEE，以支持额定的栅极驱动峰值拉电流功能。 |

| OUT   | 6    | O               | 栅极驱动输出。                                          |

| CLAMP | 7    | I               | 内部有源米勒钳位，将此引脚直接连接到功率晶体管的栅极。                      |

| VEE   | 8    | G               | 栅极驱动侧的参考地，在单电源供电中连接驱动侧参考地，在双电源供电中连接负电源轨。         |

备注：

1. P 代表电源，G 代表地，I 代表输入，O 代表输出

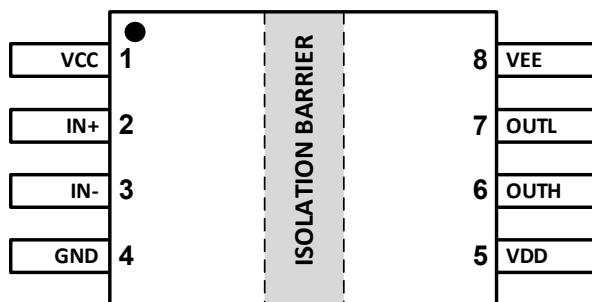

## 5.2. CA-IS3214(T)SxG 引脚功能描述

图 5-2 CA-IS3214SxG 和 CA-IS3214TSCG 引脚配置

表 5-2 引脚功能描述

| 引脚名称 | 引脚编号 | 类型 <sup>1</sup> | 描述                                               |

|------|------|-----------------|--------------------------------------------------|

| VCC  | 1    | P               | 3V 到 5.5V 的控制侧电源，推荐 1μF 的旁路电容到 GND。              |

| IN+  | 2    | I               | 同相栅极驱动控制输入，内部下拉。                                 |

| IN-  | 3    | I               | 反相栅极驱动控制输入，内部上拉。                                 |

| GND  | 4    | G               | 控制侧的输入电源和逻辑地参考。                                  |

| VDD  | 5    | P               | 栅极驱动电压的正电源，推荐 10μF 的旁路电容到 VEE，以支持额定的栅极驱动峰值拉电流功能。 |

| OUTH | 6    | O               | 栅极驱动输出拉电流。                                       |

| OUTL | 7    | O               | 栅极驱动输出灌电流。                                       |

| VEE  | 8    | G               | 栅极驱动侧的参考地，在单电源供电中连接驱动侧参考地，在双电源供电中连接负电源轨。         |

备注：

1. P 代表电源，G 代表地，I 代表输入，O 代表输出

## 6. 产品规格

### 6.1. 绝对最大额定值<sup>1</sup>

在自然通风条件下的工作温度范围内测得（除非另有说明）。

| 符号                          | 参数        | 最小值       | 最大值       | 单位 |

|-----------------------------|-----------|-----------|-----------|----|

| VCC                         | VCC – GND | -0.3      | 6         | V  |

| VDD                         | VDD – COM | -0.3      | 36        | V  |

| VEE                         | VEE – COM | -17.5     | 0.3       | V  |

| V <sub>MAX</sub>            | VDD – VEE | -0.3      | 36        | V  |

| IN+, IN-                    | 直流        | GND - 0.3 | VCC + 0.3 | V  |

| OUTH, OUTL, CLAMP           | 直流        | VEE - 0.3 | VDD + 0.3 | V  |

| T <sub>j</sub> <sup>2</sup> | 结温        | -40       | 150       | °C |

| T <sub>stg</sub>            | 贮存温度      | -65       | 150       | °C |

备注：

- 等于或超出上述绝对最大额定值可能会导致产品永久性损坏。这只是额定最值，并不能以这些条件或者在任何其它超出本技术规范操作章节中所示规格的条件下，推断产品能否正常工作。长期在超出最大额定值条件下工作会影响产品的可靠性。

- 请参考热量信息，确保结温处于正常工作范围。

### 6.2. ESD 额定值

| 符号                    | 参数                                        | 数值    | 单位 |

|-----------------------|-------------------------------------------|-------|----|

| V <sub>ESD</sub> 静电放电 | 人体模型 (HBM)，根据 ANSI/ESDA/JEDEC JS-001，所有引脚 | ±4000 | V  |

|                       | 组件充电模式 (CDM)，根据 JEDEC 规范 JESD22-C101，所有引脚 | ±2000 |    |

### 6.3. 推荐工作条件

在自然通风条件下的工作温度范围内测得（除非另有说明）

| 符号             | 参数                   | 最小值          | 最大值       | 单位 |

|----------------|----------------------|--------------|-----------|----|

| VCC            | VCC – GND            | 3.0          | 5.5       | V  |

| VDD            | VDD – VEE            | CA-IS3214xBx | 9         | V  |

|                |                      | CA-IS3214xCx | 13.5      |    |

| IN+, IN-       | CA-IS3214TSCG，参考 GND | 输入电压逻辑高电平    | 2.4       | V  |

|                |                      | 输入电压逻辑低电平    | 0         |    |

| 其它料号，参考 GND    |                      | 输入电压逻辑高电平    | 0.7 × VCC | V  |

|                |                      | 输入电压逻辑低电平    | 0         |    |

| T <sub>A</sub> | 环境温度                 | -40          | 125       | °C |

| T <sub>j</sub> | 结温                   | -40          | 150       | °C |

### 6.4. 热量信息

| 符号               | 热量表         | 封装类型         | 单位   |

|------------------|-------------|--------------|------|

|                  |             | SOIC8-WB (G) |      |

| R <sub>θJA</sub> | 结至环境的热阻     | 110          | °C/W |

| R <sub>θJC</sub> | 结至外壳（顶部）的热阻 | 51.7         | °C/W |

## 6.5. 隔离特性

| 参数                                                     | 测试条件                                                                                                                                                                           | 数值                | 单位               |

|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------------------|

|                                                        |                                                                                                                                                                                | SOIC8-WB (G)      |                  |

| CLR 外部气隙 (间隙) <sup>1</sup>                             | 端子间的最短隔空距离                                                                                                                                                                     | >8.2              | mm               |

| CPG 外部爬电距离 <sup>1</sup>                                | 端子之间沿壳体最短距离                                                                                                                                                                    | >8.2              | mm               |

| DTI 隔离距离                                               | 最小内部间隙 (内部距离)                                                                                                                                                                  | >24               | μm               |

| CTI 相对漏电指数                                             | DIN EN 60112 (VDE 0303-11); IEC 60112                                                                                                                                          | >600              | V                |

| 材料组                                                    | 依据 IEC 60664-1                                                                                                                                                                 | I                 |                  |

| IEC 60664-1 过压类别                                       | 额定市电电压≤ 300V <sub>RMS</sub>                                                                                                                                                    | I-IV              |                  |

|                                                        | 额定市电电压≤ 600V <sub>RMS</sub>                                                                                                                                                    | I-IV              |                  |

|                                                        | 额定市电电压≤ 1000V <sub>RMS</sub>                                                                                                                                                   | I-III             |                  |

| <b>DIN V VDE V 0884-11 (VDE V 0884-11)<sup>2</sup></b> |                                                                                                                                                                                |                   |                  |

| V <sub>IORM</sub> 最大重复峰值隔离电压                           | 交流电压 (双极)                                                                                                                                                                      | 2121              | V <sub>PK</sub>  |

| V <sub>IOWM</sub> 最大工作隔离电压                             | 交流电压; 时间相关的介质击穿 (TDDB) 测试                                                                                                                                                      | 1500              | V <sub>RMS</sub> |

|                                                        | 直流电压                                                                                                                                                                           | 2121              | V <sub>DC</sub>  |

| V <sub>IOTM</sub> 最大瞬态隔离电压                             | V <sub>TEST</sub> = V <sub>IOTM</sub> , t = 60s (认证)<br>V <sub>TEST</sub> = 1.2 × V <sub>IOTM</sub> , t = 1s (100% 量产测试)                                                       | 8000              | V <sub>PK</sub>  |

| V <sub>IMP</sub> 最大脉冲电压                                | 测试方法根据 IEC 62368-1, 1.2/50μs 波形                                                                                                                                                | 8000              | V <sub>PK</sub>  |

| V <sub>IOSM</sub> 最大浪涌隔离电压 <sup>3</sup>                | 测试方法根据 IEC 62368-1, 1.2/50μs 波形, V <sub>IOSM</sub> ≥ 1.3 × V <sub>IMP</sub> , 在油中测试 (认证)                                                                                       | 12800             | V <sub>PK</sub>  |

| q <sub>pd</sub> 表征电荷 <sup>4</sup>                      | 方法 a, 输入/输出安全测试子类 2/3 后, V <sub>ini</sub> = V <sub>IOTM</sub> , t <sub>ini</sub> = 60s; V <sub>pd(m)</sub> = 1.2 × V <sub>IORM</sub> , t <sub>m</sub> = 10s                    | ≤5                | pC               |

|                                                        | 方法 a, 环境测试子类 1 后, V <sub>ini</sub> = V <sub>IOTM</sub> , t <sub>ini</sub> = 60s; V <sub>pd(m)</sub> = 1.6 × V <sub>IORM</sub> , t <sub>m</sub> = 10s                           | ≤5                |                  |

|                                                        | 方法 b1, 常规测试 (100% 量产测试) 和前期预处理 (抽样测试)<br>V <sub>ini</sub> = V <sub>IOTM</sub> , t <sub>ini</sub> = 1s;<br>V <sub>pd(m)</sub> = 1.875 × V <sub>IORM</sub> , t <sub>m</sub> = 1s | ≤5                |                  |

| C <sub>IO</sub> 电容, 输入到输出 <sup>5</sup>                 | V <sub>IO</sub> = 0.5 × sin (2πft), f = 1MHz                                                                                                                                   | ~1.2              | pF               |

| R <sub>IO</sub> 绝缘电阻, 输入到输出 <sup>5</sup>               | V <sub>IO</sub> = 500V, T <sub>A</sub> = 25°C                                                                                                                                  | >10 <sup>12</sup> | Ω                |

|                                                        | V <sub>IO</sub> = 500V, 100°C ≤ T <sub>A</sub> ≤ 125°C                                                                                                                         | >10 <sup>11</sup> |                  |

|                                                        | V <sub>IO</sub> = 500 V at T <sub>S</sub> = 150°C                                                                                                                              | >10 <sup>9</sup>  |                  |

| 污染度                                                    |                                                                                                                                                                                | 2                 |                  |

| 气候类别                                                   |                                                                                                                                                                                | 40/125/21         |                  |

| <b>UL 1577</b>                                         |                                                                                                                                                                                |                   |                  |

| V <sub>ISO</sub> 最大隔离电压                                | V <sub>TEST</sub> = V <sub>ISO</sub> , t = 60s (认证),<br>V <sub>TEST</sub> = 1.2 × V <sub>ISO</sub> , t = 1s (100% 量产测试)                                                        | 5700              | V <sub>RMS</sub> |

备注:

- 根据应用的特定设备隔离标准应用爬电距离和间隙要求。注意保持电路板设计的爬电距离和间隙距离, 以确保印刷电路板上隔离器的安装焊盘不会缩短该距离。在某些情况下印刷电路板上的爬电距离和间隙相等。在印刷电路板上插入凹槽的技术有助于提高这些指标。

- 该标准仅适用于安全等级内的安全电气绝缘。应通过适当的保护电路确保符合安全等级。

- 测试在空气或油中进行, 以确定隔离屏障的固有浪涌抗扰度。

- 表征电荷是由局部放电引起的放电电荷 (pd)。

- 栅两侧的所有引脚连接在一起, 形成双端子器件。

## 6.6. 安全相关认证

| VDE (申请中)                                                                                                   | UL (申请中)                         | CQC                        | TUV (申请中)                                                                      |

|-------------------------------------------------------------------------------------------------------------|----------------------------------|----------------------------|--------------------------------------------------------------------------------|

| 根据 DIN EN IEC 60747-17 (VDE 0884-17):2021-10; EN IEC 60747-17:2020+AC:2021 认证                               | 根据 UL 1577 器件认可程序认证              | 根据 GB4943.1-2022 认证        | 根据 EN 62368-1 和 EN 61010-1 认证                                                  |

| 加强绝缘 (SOIC8-WB)：<br>VIOTM: 8000V <sub>PK</sub><br>VIORM: 2121V <sub>PK</sub><br>VIOSM: 12800V <sub>PK</sub> | 单一绝缘电压保护<br>5700V <sub>RMS</sub> | 加强绝缘<br>(仅适用于海拔 5000 米及以下) | EN 62368-1:<br>5700V <sub>RMS</sub><br><br>EN 61010-1:<br>5700V <sub>RMS</sub> |

| 证书编号：<br>申请中                                                                                                | 证书编号：<br>申请中                     | 证书编号：<br>COC24001452438    | 客户参考编号：<br>2253313                                                             |

## 6.7. 额定功率

| 符号              | 参数            | 测试条件                                                                                                                    | 最小值 | 典型值  | 最大值 | 单位 |

|-----------------|---------------|-------------------------------------------------------------------------------------------------------------------------|-----|------|-----|----|

| P <sub>D</sub>  | 输入端和输出端最大耗散功率 | VCC = 5V, VDD - COM = 20V, COM - VEE = 5V,<br>IN+/- = 5V, 150kHz、50% 占空比, C <sub>L</sub> = 2.2nF, T <sub>A</sub> = 25°C |     | 1.05 |     | W  |

| P <sub>D1</sub> | 最大输入耗散功率      |                                                                                                                         |     | 0.05 |     | W  |

| P <sub>D2</sub> | 最大输出耗散功率      |                                                                                                                         |     | 1    |     | W  |

## 6.8. 安全限值

| 符号             | 参数       | 测试条件                                                                                       | 最小值 | 典型值 | 最大值  | 单位 |

|----------------|----------|--------------------------------------------------------------------------------------------|-----|-----|------|----|

| I <sub>S</sub> | 安全输出供电电流 | R <sub>θJA</sub> = 110°C/W, VDD - VEE = 15V, T <sub>J</sub> = 150°C, T <sub>A</sub> = 25°C | 输出侧 |     | 72   | mA |

|                |          | R <sub>θJA</sub> = 110°C/W, VDD - VEE = 30V, T <sub>J</sub> = 150°C, T <sub>A</sub> = 25°C | 输出侧 |     | 36   |    |

| P <sub>S</sub> | 安全输出功耗   | R <sub>θJA</sub> = 110°C/W, T <sub>J</sub> = 150°C, T <sub>A</sub> = 25°C                  | 输入侧 |     | 50   | mW |

|                |          |                                                                                            | 输出侧 |     | 1086 |    |

|                |          |                                                                                            | 总功耗 |     | 1136 |    |

| T <sub>S</sub> | 最大安全工作温度 |                                                                                            |     |     | 150  | °C |

## 6.9. 电气特性

除非有额外说明，本表格典型值都是在  $V_{CC} = 3.3V$ ,  $T_A = 25^\circ C$ ,  $V_{DD} - V_{EE} = 15V$  条件下的结果。所有最大值和最小值在  $V_{CC} = 3.3V$  或  $5V$ ,  $V_{DD} - V_{EE} = 15V \sim 33V$ ,  $-40^\circ C < T_J < 150^\circ C$  条件下的测试结果<sup>1</sup>。

| 符号                       | 参数                            | 测试条件                                                   | 最小值  | 典型值  | 最大值  | 单位        |

|--------------------------|-------------------------------|--------------------------------------------------------|------|------|------|-----------|

| <b>VCC UVLO 阈值和延迟时间</b>  |                               |                                                        |      |      |      |           |

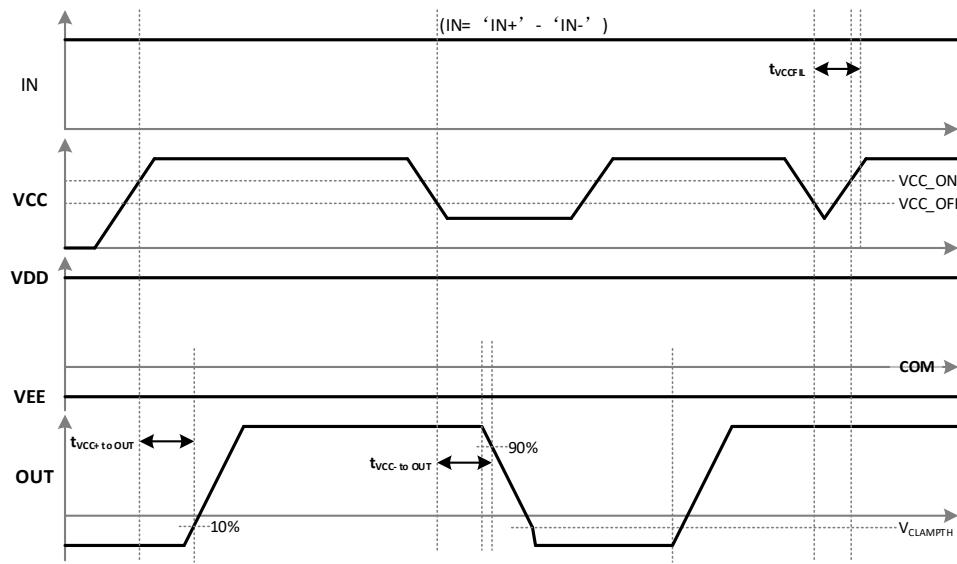

| $V_{VCC\_ON}$            | VCC – GND 欠压锁定                |                                                        | 2.55 | 2.7  | 2.85 | V         |

| $V_{VCC\_OFF}$           |                               |                                                        | 2.35 | 2.5  | 2.65 |           |

| $V_{VCC\_HYS}$           |                               |                                                        | 0.2  |      |      |           |

| $t_{VCCFIL}$             | VCC UVLO 抗尖峰时间                |                                                        | 5    |      |      | $\mu s$   |

| $t_{VCC+ \text{to OUT}}$ | VCC UVLO+ 到输出上升延时             | $IN+ = V_{CC}$ , $IN- = GND$                           | 22   | 60   |      |           |

| $t_{VCC- \text{to OUT}}$ | VCC UVLO- 到输出下降延时             |                                                        | 7    | 15   |      |           |

| <b>VDD UVLO 阈值</b>       |                               |                                                        |      |      |      |           |

| $V_{VDD\_ON}$            | VDD 欠压锁定<br>(B Version)       |                                                        | 7.3  | 8.1  | 8.9  | V         |

| $V_{VDD\_OFF}$           |                               |                                                        | 6.7  | 7.4  | 8.2  |           |

| $V_{VDD\_HYS}$           |                               |                                                        | 0.7  |      |      |           |

| <b>VDD UVLO 延迟时间</b>     |                               |                                                        |      |      |      |           |

| $t_{VDDFIL}$             | VDD UVLO 抗尖峰脉冲时间              |                                                        | 9    |      |      | $\mu s$   |

| $t_{VDD+ \text{to OUT}}$ | VDD UVLO+ 到输出上升延时             | $IN+ = V_{CC}$ , $IN- = GND$                           | 10   | 20   |      |           |

| $t_{VDD- \text{to OUT}}$ | VDD UVLO- 到输出下降延时             |                                                        | 10   | 20   |      |           |

| <b>VCC, VDD 静态电流</b>     |                               |                                                        |      |      |      |           |

| $I_{VCCQ}$               | VCC 静态电流                      | OUTH = High                                            | 1.15 | 2.0  |      | mA        |

|                          |                               | OUTL = Low                                             | 0.55 | 1.0  |      |           |

| $I_{VDDQ}$               | VDD 静态电流                      | OUT = High/Low                                         | 1.44 | 2.5  |      |           |

| <b>逻辑输入 IN+, IN-</b>     |                               |                                                        |      |      |      |           |

| $V_{INH}$                | 输入电压逻辑高阈值                     | CA-IS3214TSCG, $V_{CC} = 3.3V$                         | 1.50 | 2.4  |      | V         |

| $V_{INL}$                | 输入电压逻辑低阈值                     |                                                        | 0.8  | 1.16 |      |           |

| $V_{INHYS}$              | 输入阈值迟滞                        |                                                        | 0.32 |      |      |           |

| $V_{INH}$                | 输入电压逻辑高阈值                     | 其它料号, $V_{CC} = 3.3V$                                  | 1.94 | 2.31 |      | V         |

| $V_{INL}$                | 输入电压逻辑低阈值                     |                                                        | 0.99 | 1.58 |      |           |

| $V_{INHYS}$              | 输入阈值迟滞                        |                                                        | 0.36 |      |      |           |

| $R_{IND}$                | 输入引脚下拉电阻                      | $IN+ = V_{CC}$                                         | 27   | 33   | 39   | $k\Omega$ |

| $R_{INU}$                | 输入引脚上拉电阻                      | $IN- = GND$                                            | 144  | 180  | 216  | $k\Omega$ |

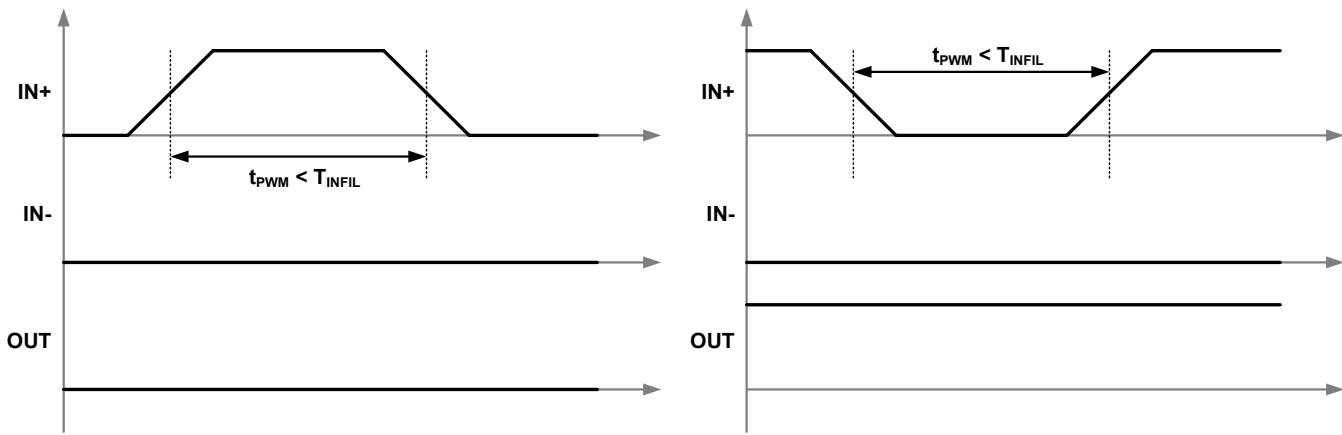

| $t_{INFIL}$              | 抗尖峰脉冲(开启和关闭)滤波时间 <sup>2</sup> | $f = 50kHz$                                            | 15   | 30   | 50   | ns        |

| <b>栅极驱动</b>              |                               |                                                        |      |      |      |           |

| $I_{OUTH}$               | 峰值拉电流                         | $C_{VDD} = 10\mu F$ , $C_L = 0.18\mu F$ , $f_S = 1kHz$ | 10   |      |      | A         |

| $I_{OUTL}$               | 峰值灌电流                         | $C_{VEE} = 10\mu F$ , $C_L = 0.18\mu F$ , $f_S = 1kHz$ | 10   |      |      | A         |

| $R_{OUTH}$               | 上拉电阻                          | $I_{OUT} = -0.2A$                                      | 0.5  |      |      | $\Omega$  |

| $R_{OUTL}$               | 下拉电阻                          | $I_{OUT} = 0.2A$                                       | 0.3  |      |      | $\Omega$  |

## 电气特性(接上页)

除非有额外说明, 本表格典型值都是在  $V_{CC} = 3.3V$ ,  $T_A = 25^\circ C$ ,  $VDD - VEE = 15V$  条件下的结果。所有最大值和最小值在  $V_{CC} = 3.3V$  或  $5V$ ,  $VDD - VEE = 15V \sim 33V$ ,  $-40^\circ C < T_J < 150^\circ C$  条件下的测试结果<sup>1</sup>。

| 符号                           | 参数                      | 测试条件                                                      | 最小值 | 典型值         | 最大值 | 单位       |

|------------------------------|-------------------------|-----------------------------------------------------------|-----|-------------|-----|----------|

| $V_{OUTH}$                   | 输出高电平                   | $I_{OUT} = -0.2A$ , $VDD = 18V$                           |     | 17.90       |     | V        |

| $V_{OUTL}$                   | 输出低电平                   | $I_{OUT} = 0.2A$                                          |     | 60          |     | mV       |

| <b>主动下拉</b>                  |                         |                                                           |     |             |     |          |

| $V_{OUTPD}$                  | 主动下拉 OUTL               | $I_{OUTL} = 0.5A$ , $VDD = OPEN$ , $VEE = COM$            |     | 2.0         |     | V        |

| <b>内部有源米勒钳位 (CA-IS3214M)</b> |                         |                                                           |     |             |     |          |

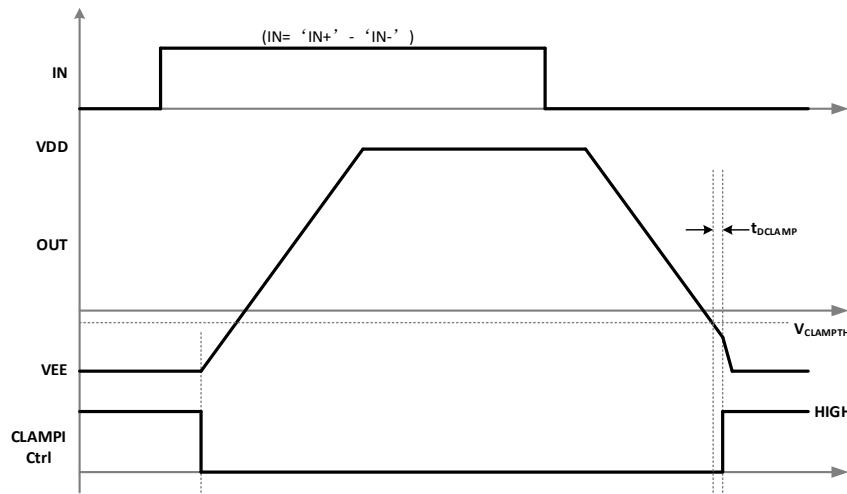

| $V_{CLAMPTH}$                | 米勒钳位阈值电压                | 参考 $VEE$                                                  | 1.5 | 2.0         | 2.5 | V        |

| $V_{CLAMP}$                  | 输出低钳位电压                 | $I_{CLAMP} = 1A$                                          |     | $VEE + 0.6$ |     | V        |

| $I_{CLAMP}$                  | 输出低钳位峰值电流               | $V_{CLAMP} = 0V$ , $VEE = -4V$                            |     | 5           |     | A        |

| $R_{CLAMP}$                  | 米勒钳位下拉电阻                | $I_{CLAMP} = 0.2A$                                        |     | 0.6         |     | $\Omega$ |

| $t_{DCLAMP}$                 | 米勒钳位开通延迟时间 <sup>2</sup> | $C_L = 1.8nF$ , 见图 7-4                                    |     | 20          | 50  | ns       |

| <b>短路钳位<sup>2</sup></b>      |                         |                                                           |     |             |     |          |

| $V_{CLP-OUTH}$               | $V_{OUTH} - VDD$        | $OUT = Low$ , $I_{OUT(H)} = 500mA$ , $t_{CLP} = 10\mu s$  |     | 0.65        |     | V        |

| $V_{CLP-OUTL}$               | $V_{OUTL} - VDD$        | $OUT = High$ , $I_{OUT(L)} = 500mA$ , $t_{CLP} = 10\mu s$ |     | 1.2         |     | V        |

| $V_{CLP-CLAMP}$              | $V_{CLAMP} - VDD$       | $OUT = High$ , $I_{CLAMP} = 500mA$ , $t_{CLP} = 10\mu s$  |     | 1.2         |     | V        |

| 备注:                          |                         |                                                           |     |             |     |          |

| 1.                           | 电流流入器件引脚为正, 流出为负。       |                                                           |     |             |     |          |

| 2.                           | 由设计和 Bench 保证。          |                                                           |     |             |     |          |

## 6.10. 开关特性

除非有额外说明, 本表格典型值都是在  $V_{CC} = 3.3V$ ,  $T_A = 25^\circ C$ ,  $VDD - VEE = 15V$  条件下的结果。所有最大值和最小值在  $V_{CC} = 3.3V$  或  $5V$ ,  $VDD - VEE = 15V \sim 33V$ ,  $-40^\circ C < T_J < 150^\circ C$  条件下的测试结果。

| 符号          | 参数                             | 测试条件                                      | 最小值 | 典型值 | 最大值 | 单位         |

|-------------|--------------------------------|-------------------------------------------|-----|-----|-----|------------|

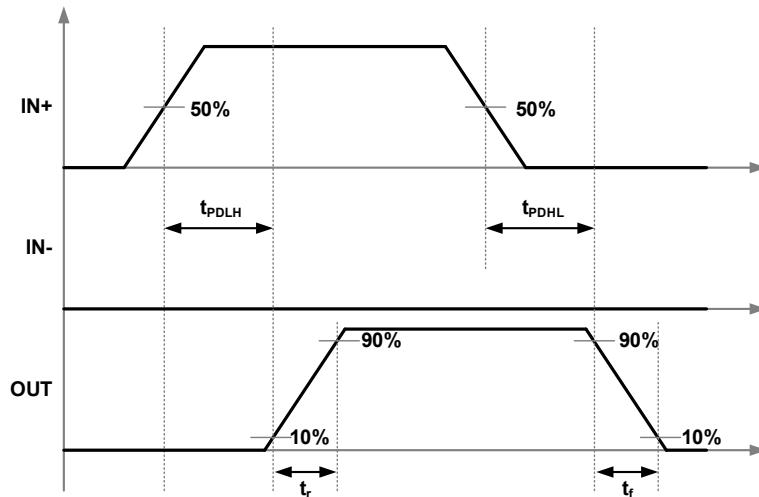

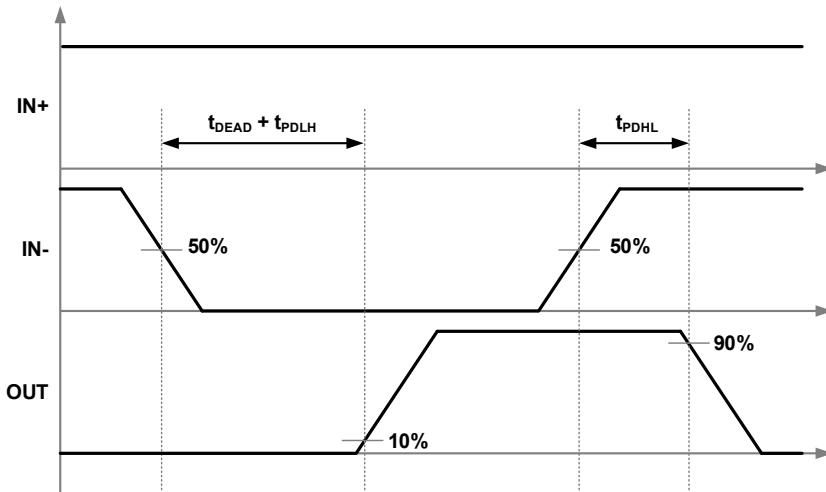

| $t_{PDHL}$  | 传播延迟时间 - 从高到低                  | $C_L = 1nF$ , 见图 7-1                      | 60  | 80  | 120 | ns         |

| $t_{PDLH}$  | 传播延迟时间 - 从低到高                  |                                           | 60  | 75  | 120 |            |

| $t_{PWD}$   | 脉冲宽度失真 $ t_{PDHL} - t_{PDLH} $ | $C_L = 1nF$ , 见图 7-1                      |     |     | 15  |            |

| $t_{sk-pp}$ | 器件与器件之间的延时偏移                   | 上升沿或者下降沿传播延迟                              |     |     | 15  |            |

| $t_r$       | 驱动上升时间                         | $C_L = 1nF$ , 见图 7-1                      |     | 10  |     |            |

| $t_f$       | 驱动下降时间                         |                                           |     | 10  |     |            |

| $f_{MAX}$   | 最大开关频率                         |                                           |     |     | 1   | MHz        |

| $t_{DEAD}$  | 直通死区保护时间                       | 见图 7-2                                    |     | 200 |     | ns         |

| CMTI        | 共模瞬态抗扰度                        | $IN+ = High$ , $IN- = Low$ , 见图 7-7~图 7-8 | 150 |     |     | $kV/\mu s$ |

|             |                                | $IN+ = Low$ , $IN- = Low$ , 见图 7-7~图 7-8  | 150 |     |     | $kV/\mu s$ |

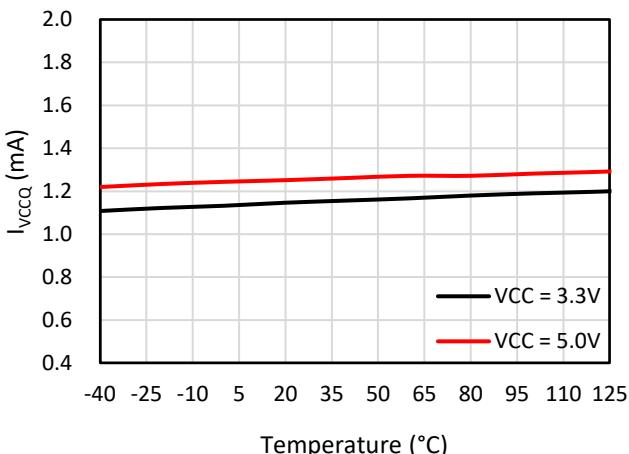

## 6.11. 典型特性

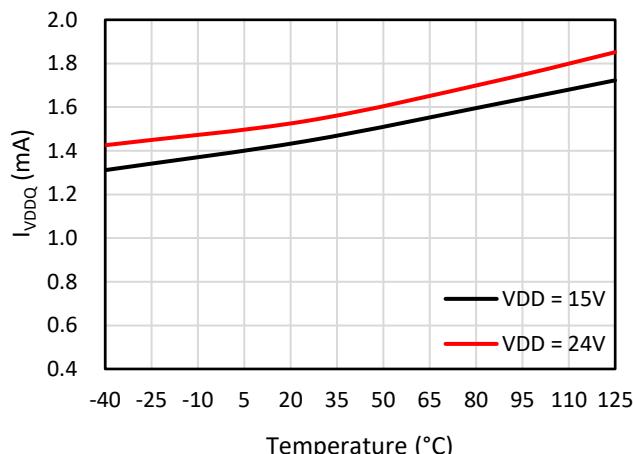

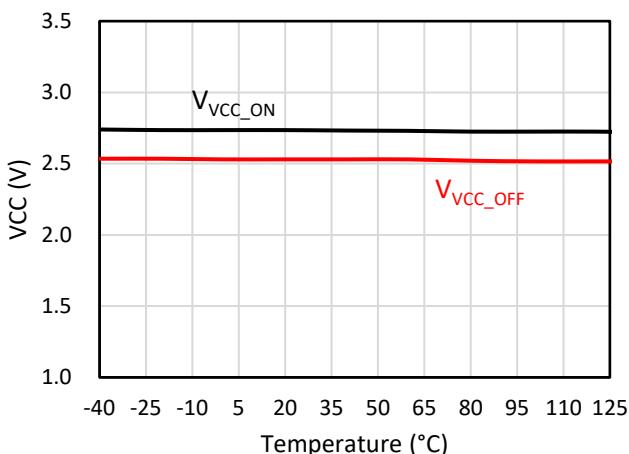

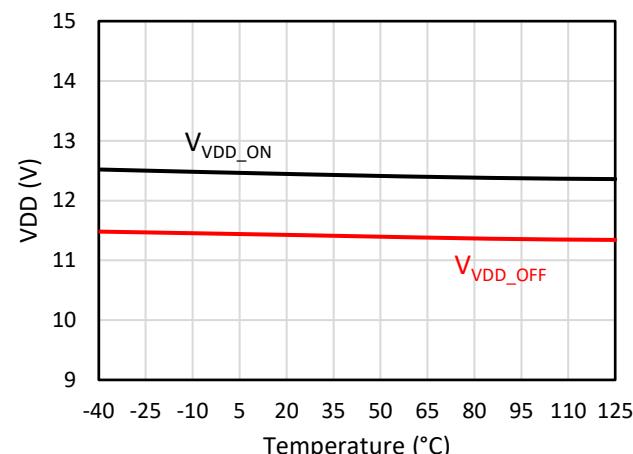

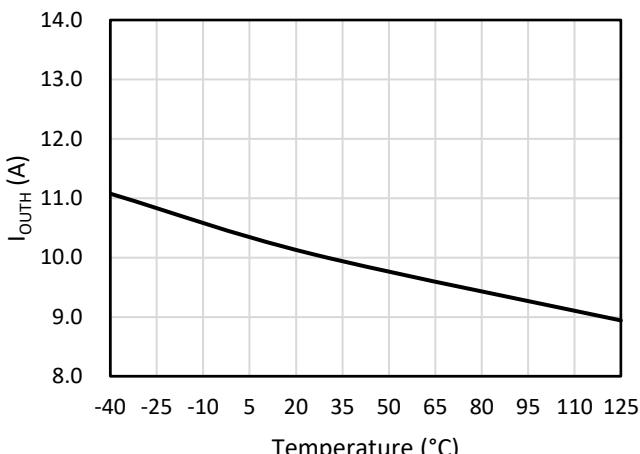

除非有额外说明，典型值测试条件为  $V_{CC} = 3.3V$ ,  $T_A = 25^\circ C$ ,  $V_{DD} - V_{EE} = 15V$ 。

图 6-1 VCC 静态电流 vs. 温度

图 6-2 VDD 静态电流 vs. 温度

图 6-3 VCC UVLO vs. 温度

图 6-4 VDD UVLO vs. 温度 (C Version)

图 6-5 峰值拉电流 vs. 温度

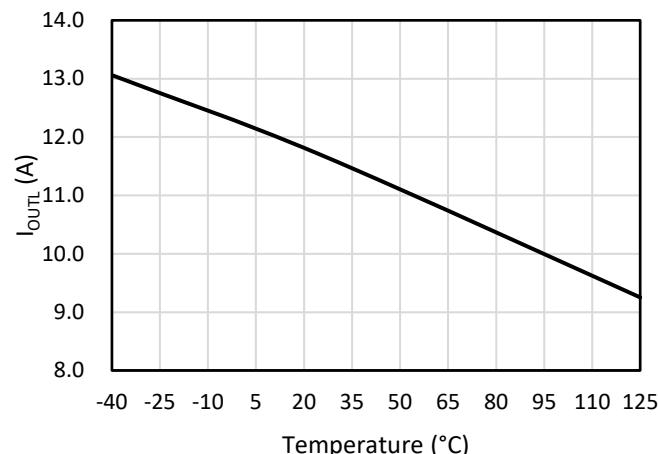

图 6-6 峰值灌电流 vs. 温度

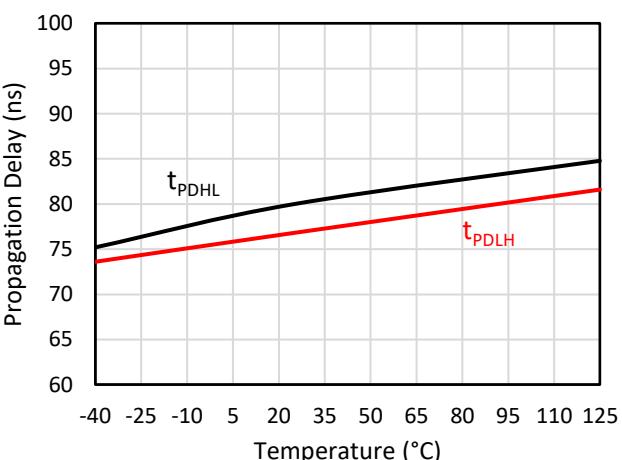

图 6-7 传输延迟时间 vs. 温度

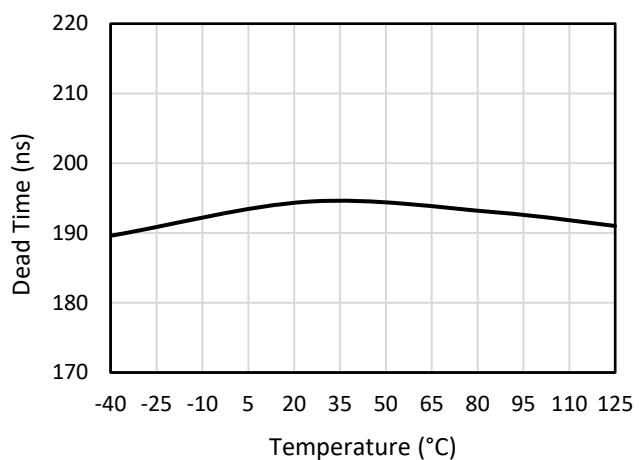

图 6-8 内置死区时间 vs. 温度

## 7. 参数测量信息

### 7.1. 传播延迟

图 7-1 显示了同相配置的传播延迟测量。图 7-2 显示了反相配置的传播延迟测量。

图 7-1 同相逻辑传播延迟测量

图 7-2 反相逻辑传播延迟测量

## 7.2. 输入抗脉冲尖峰滤波器

为了提高栅极驱动器在输入引脚（即 IN+）上对短暂和意外小脉冲尖峰噪声的抑制能力，器件设计了 30ns 输入抗脉冲尖峰滤波器来过滤掉瞬态波动，以确保不会产生错误输出响应或意外驱动故障。当 IN+ 的 PWM 脉冲小于输入抗脉冲尖峰滤波器宽度  $T_{INFIL}$  时，OUT 驱动信号上将没有响应。图 7-3 显示 IN+ 引脚 ON 和 OFF 时抗脉冲尖峰滤波效果。

图 7-3 IN+ ON/OFF 滤波器

## 7.3. 有源米勒钳位 (CA-IS3214Mxx)

对于具有单极偏置电源，或双极电源且有较小的负的关断电压的栅极驱动器应用，有源米勒钳位可以帮助添加一个额外的低阻抗路径分流米勒电流，并防止高  $dv/dt$  通过米勒电容导致意外功率管导通。图 7-4 显示了器件内部米勒钳位功能的时序图。

图 7-4 内置有源米勒钳位功能的时序图

## 7.4. 欠压锁定 (UVLO)

UVLO 是设计用于在 VCC (控制侧电源) 和 VDD (驱动侧电源) 发生电源故障时保护系统的关键保护功能之一。

### 7.4.1. VCC UVLO

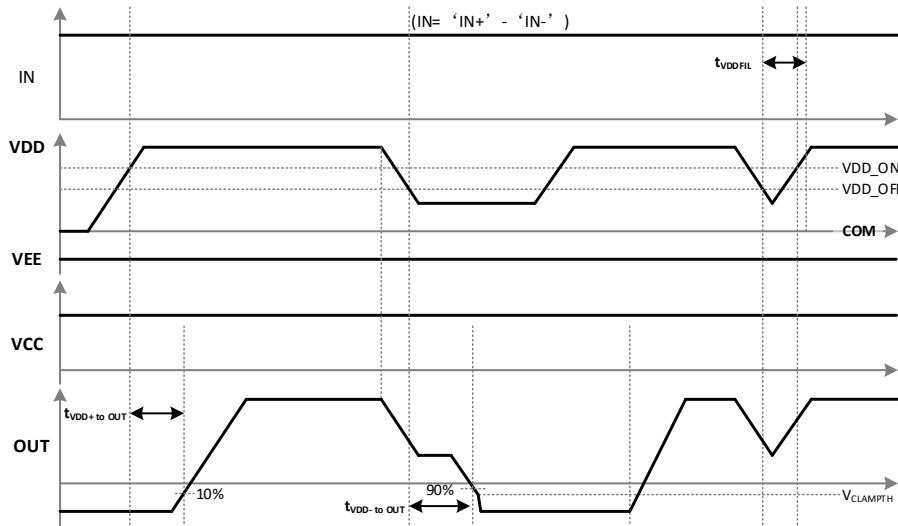

图 7-5 示意说明 UVLO 开/关阈值、抗尖峰脉冲滤波器、响应时间时序图。

图 7-5 VCC UVLO 保护时序图

#### 7.4.2. VDD UVLO

示意说明 UVLO 开/关阈值、抗尖峰脉冲滤波器、响应时间、时序图。

图 7-6 VDD UVLO 保护时序图

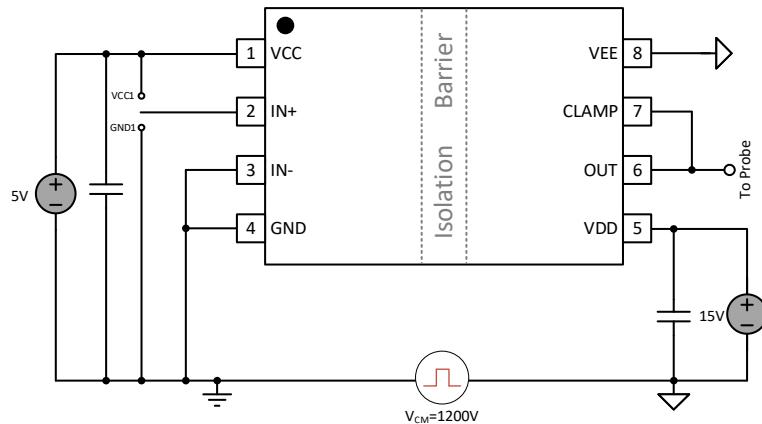

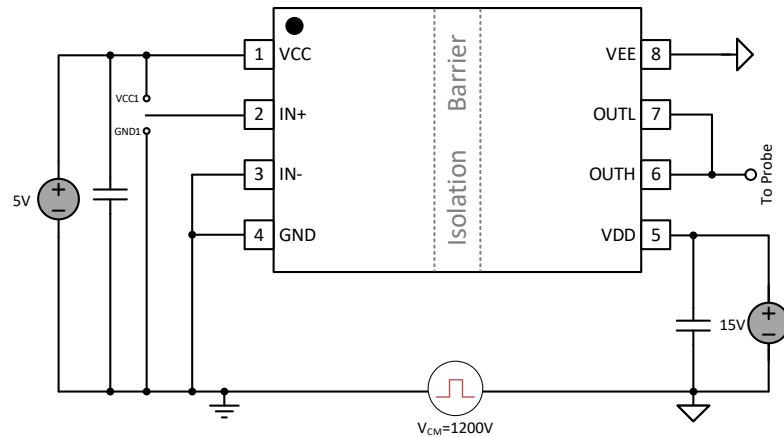

#### 7.5. CMTI 测试

图 7-7 和图 7-8 显示了 CA-IS3214 系列产品的 CMTI 测试方案。

图 7-7 CMTI 测试方案 (CA-IS3214MxG)

图 7-8 CMTI 测试方案 (CA-IS3214SxG 和 CA-IS3214TSCG)

## 8. 详细说明

### 8.1. 概述

CA-IS3214 是一系列基于电容隔离的单通道栅极驱动器，可用于驱动 MOSFET、IGBT、SiC MOSFET 等功率器件。该驱动器具有出色的动态性能和高可靠性，同时具有高达 10A/10A 峰值的拉/灌电流能力。

CA-IS3214 通过  $\text{SiO}_2$  电容隔离技术实现控制侧与驱动侧的电气隔离，支持  $1.5\text{kV}_{\text{RMS}}$  的隔离工作电压、 $12.8\text{kV}_{\text{PK}}$  浪涌抗扰度，额定工作电压下隔离栅寿命超过 40 年，同时具有良好的器件一致性以及  $>150\text{kV}/\mu\text{s}$  的共模瞬态抗扰度（CMTI）。CA-IS3214 具有控制和驱动侧电源 UVLO 功能，同时针对 SiC 和 IGBT 开关行为进行了优化，并提高了可靠性。此外，CA-IS3214MxxG 内置 5A 峰值电流有源米勒钳位；CA-IS3214SxG 和 CA-IS3214TSCG 具有 OUTH 和 OUTL 分离输出配置。

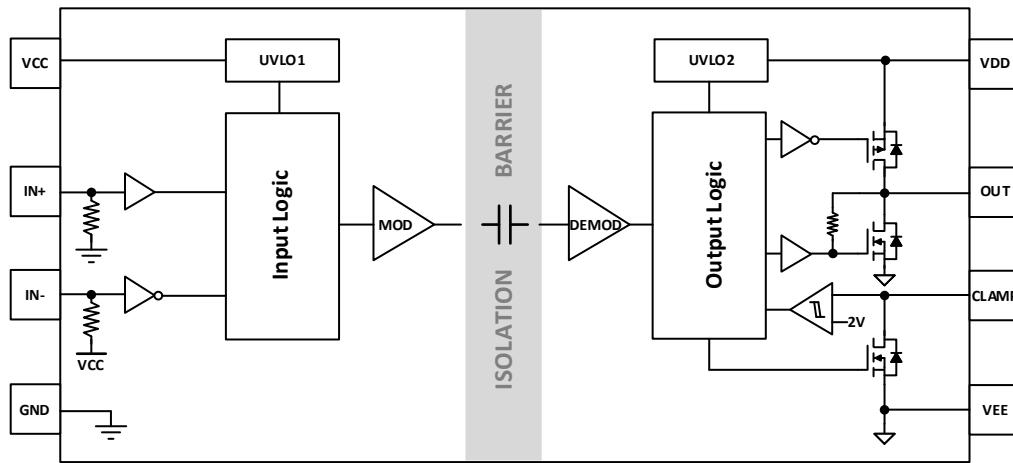

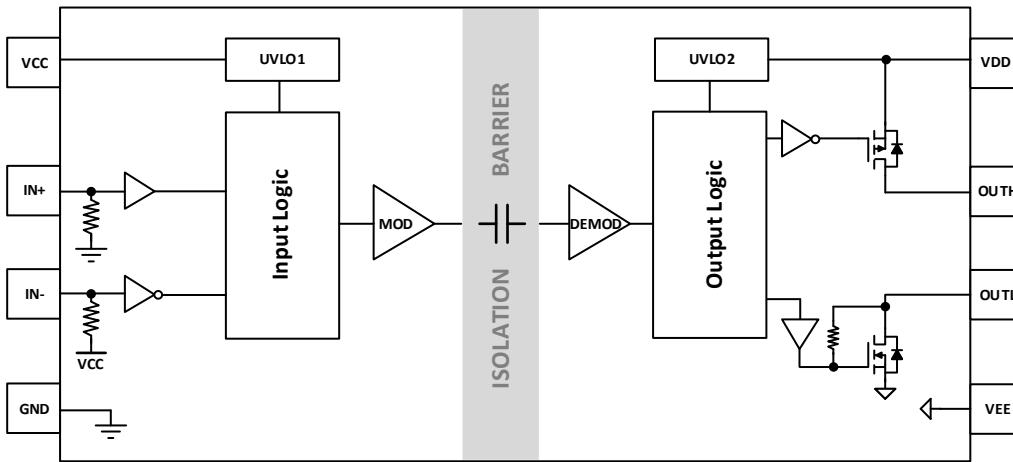

### 8.2. 功能框图

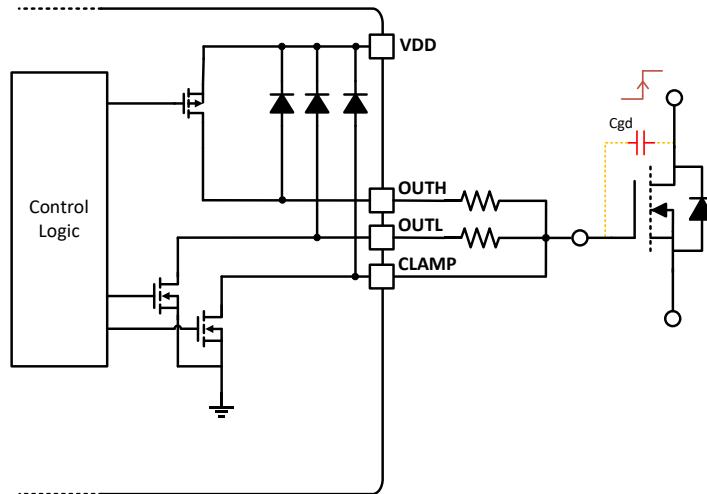

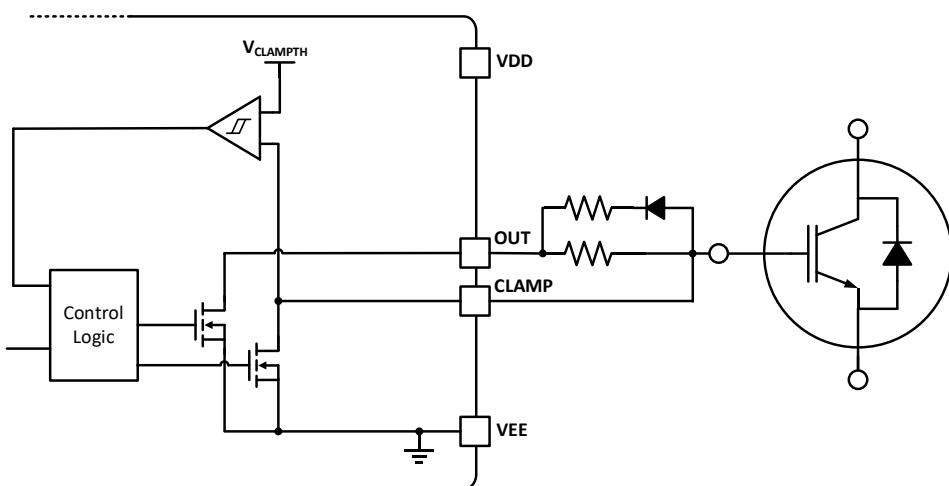

图 8-1 CA-IS3214MxG 功能框图

图 8-2 CA-IS3214SxG 和 CA-IS3214TSCG 功能框图

### 8.3. 特性描述

CA-IS3214 的控制侧电源 VCC 可支持 3V 到 5.5V 的宽电压范围。驱动侧支持单极性电源和双极性电源，VDD 到 VEE 支持 13V 到 33V 的宽电压范围。在 SiC 和 IGBT 应用中，由于快速的  $dv/dt$  和米勒效应，可能导致功率管误导通现象，此时负压关断功率器件可以提高可靠性。故负压电源供电也尤其重要。

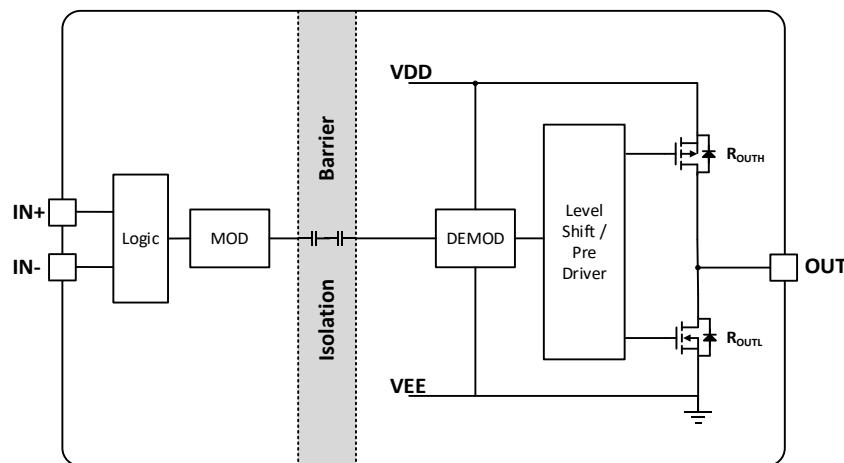

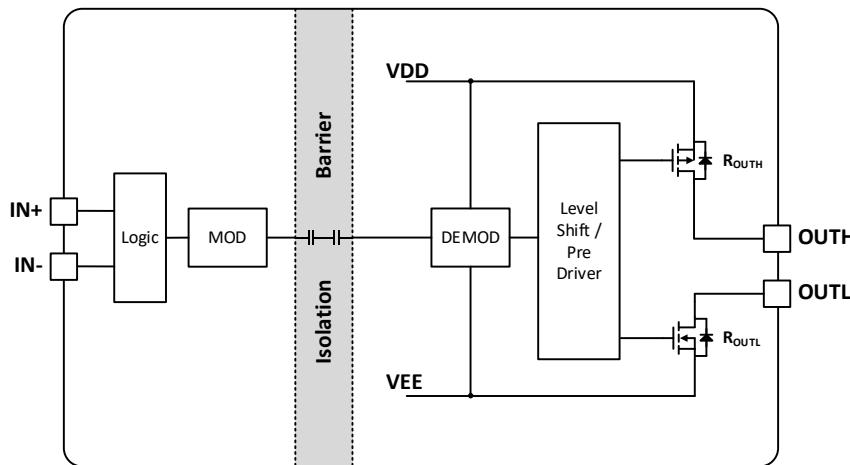

### 8.4. 驱动级

图 8-3 棚极驱动输出级 (CA-IS3214MxG)

图 8-4 棚极驱动输出级 (CA-IS3214SxG 和 CA-IS3214TSCG)

CA-IS3214 的驱动器输出级集成了一个上拉结构和一个下拉结构，具有高达 10A/10A 峰值的拉/灌电流能力，可直接控制外部晶体管 (SiC MOSFET 和 IGBT 模块)。图 8-3 和图 8-4 显示了输出级电路，上拉电路仅由一个 P 沟道 MOSFET 构成， $R_{OUTH}$  为 PMOS 的导通电阻；下拉电路则由一个 n 沟道 MOSFET 简单构成， $R_{OUTL}$  是 NMOS 的导通电阻。

OUT (CA-IS3214MxG) 或 OUTL (CA-IS3214SxG 和 CA-IS3214TSCG) 的电压通过下拉 NMOS 被拉到 VEE，以关闭外部功率晶体管。这种极低的下拉电阻  $R_{OUTL}$  不仅能实现快速吸收电流、缩短关断时间，而且还能在考虑到米勒效应的情况下提高抗噪能力。

由于输出级 MOSFET 的导通阻抗非常低，CA-IS3214 隔离栅极驱动器可以提供轨到轨输出 (输出电压摆幅在 VDD 和 VEE 之间)。

## 8.5. 保护功能

### 8.5.1. VCC 和 VDD 欠压锁定 (UVLO)

CA-IS3214 实现了控制侧电源 VCC 和驱动侧电源 VDD 的内部 UVLO 保护功能。当电源电压低于阈值电压时，驱动输出保持为低。只有当 VCC 和 VDD 都高于 UVLO 阈值状态时，输出才可以变高。UVLO 保护功能既降低了驱动自身在低供电电压条件下的功耗，又提高了功率级的效率。

CA-IS3214 的 VCC 和 VDD 均内置了抗尖峰脉冲滤波器，当电源打开或关闭瞬间，电源电压可能突然短暂地下降，该滤波器可以有效的滤除一些电源噪声干扰，防止器件的误动作。

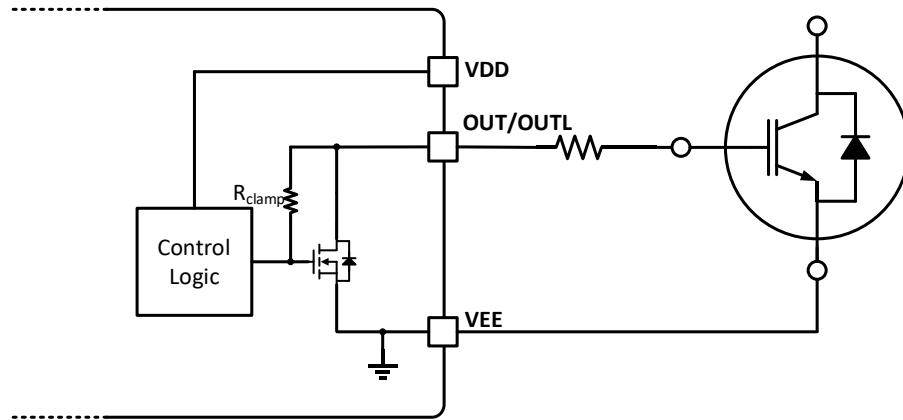

### 8.5.2. 主动下拉

CA-IS3214 具有主动下拉功能，以确保 VDD 开路时，OUT 或者 OUTL 引脚被钳位到 VEE。当 VDD 开路时，OUT/OUTH/OUTL 引脚处于高阻抗状态，主动下拉功能可防止在器件恢复控制之前错误导通。

图 8-5 主动下拉

### 8.5.3. 短路钳位

当功率器件发生短路时，米勒电容可能导致电流灌到 OUTH/OUTL/CLAMP 引脚，高  $dv/dt$  可能拉高 OUTH/OUTL/CLAMP 电压。CA-IS3214 的短路钳位功能可将 OUTH/OUTL/CLAMP 引脚电压钳位到略高于 VDD 的二极管电压，从而保护功率器件免受栅极—源极或栅极—射极过电压击穿。此功能由 OUTH/OUTL/CLAMP 到 VDD 的内部二极管实现。

图 8-6 短路钳位

#### 8.5.4. 有源米勒钳位 (CA-IS3214MxG)

在高的  $dv/dt$  应用中, 由于米勒电容效应存在, 在打开功率管的瞬间, 棚极会被  $C_{gd}$  和  $C_{gs}$  电容耦合分压, 若该电压大于栅极的阈值电压, 可能引起误导通现象, 从而损坏功率管, 因此为该电流提供一个泄放回路将变得尤为重要。

CA-IS3214MxG 内部集成低下拉阻抗 NMOS, 可以提供强大 5A 的峰值下拉能力, 使 OUTL 保持到 VEE。CLAMP 引脚与功率器件的栅极相连, 可为该电流提供泄放支路。当栅极电压低于  $V_{CLAMPTH}$ , 即比 VEE 高 2V 时, 将开启该 MOSFET, 并建立低阻抗路径以避免功率开关出现错误开启。

图 8-7 显示了内置有源米勒钳位功能。

图 8-7 有源米勒钳位

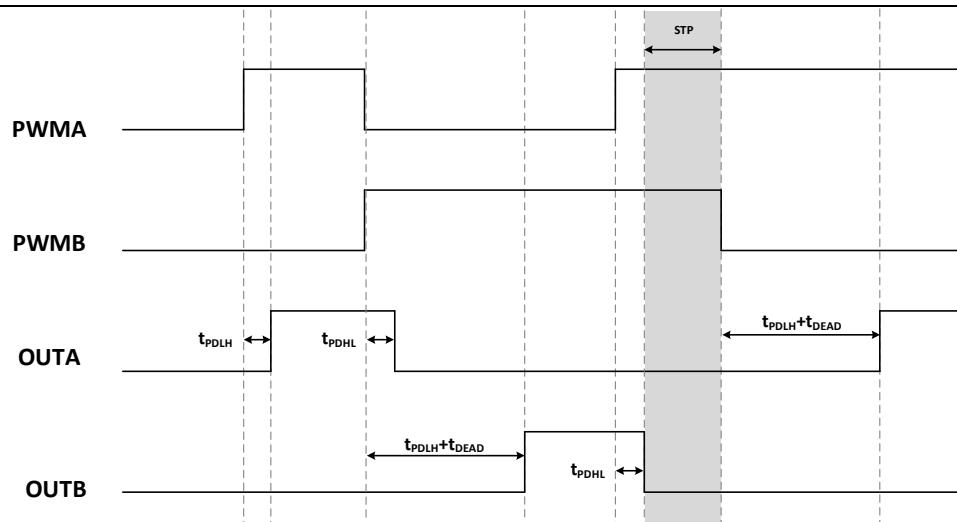

#### 8.5.5. 直通死区保护功能 (STP)

CA-IS3214 具有直通死区保护功能 (Shoot Through Protection), 可以防止应用中高边开关和低边开关同时导通导致直通情况, 把 IN-引脚短接到地可以屏蔽该功能。CA-IS3214 的内置死区时间典型值为 200ns。当外部输入驱动信号的死区时间大于内置死区时间, 驱动器的死区时间为输入死区时间; 当外部输入驱动信号的死区时间小于内置死区时间, 驱动器的死区时间为内置死区时间。直通死区保护功能的典型工作波形如图 8-8 所示, 图中 PWMA 和 PWMB 信号为半桥配置中的驱动控制信号, 详见图 9-3。

图 8-8 直通死区保护功能时序图

**8.6. 器件功能模式**

器件真值表如表 8-1 和表 8-2 所示。

表 8-1 CA-IS3214SxG 和 CA-IS3214TSCG 输入输出真值表<sup>1</sup>

| 条件                                                   | 输入  |     | 输出   |      |

|------------------------------------------------------|-----|-----|------|------|

|                                                      | IN+ | IN- | OUTH | OUTL |

| VCC $\geq V_{VCC\_ON}$ and<br>VDD $\geq V_{VDD\_ON}$ | L   | X   | Hi-Z | L    |

|                                                      | X   | H   | Hi-Z | L    |

|                                                      | H   | L   | H    | Hi-Z |

| VCC $< V_{VCC\_OFF}$ or<br>VDD $< V_{VDD\_OFF}$      | X   | X   | Hi-Z | L    |

表 8-2 CA-IS3214MxG 输入输出真值表<sup>1</sup>

| 条件                                                   | 输入  |     | 输出  |               |

|------------------------------------------------------|-----|-----|-----|---------------|

|                                                      | IN+ | IN- | OUT | CLAMP         |

| VCC $\geq V_{VCC\_ON}$ and<br>VDD $\geq V_{VDD\_ON}$ | L   | X   | L   | OUT < 2V 触发下拉 |

|                                                      | X   | H   | L   | OUT < 2V 触发下拉 |

|                                                      | H   | L   | H   | Hi-Z          |

| VCC $< V_{VCC\_OFF}$ or<br>VDD $< V_{VDD\_OFF}$      | X   | X   | L   | L             |

备注:

1. H = 高电平; L = 低电平; Hi-Z = 高阻态; X = 不相关。

## 9. 应用信息

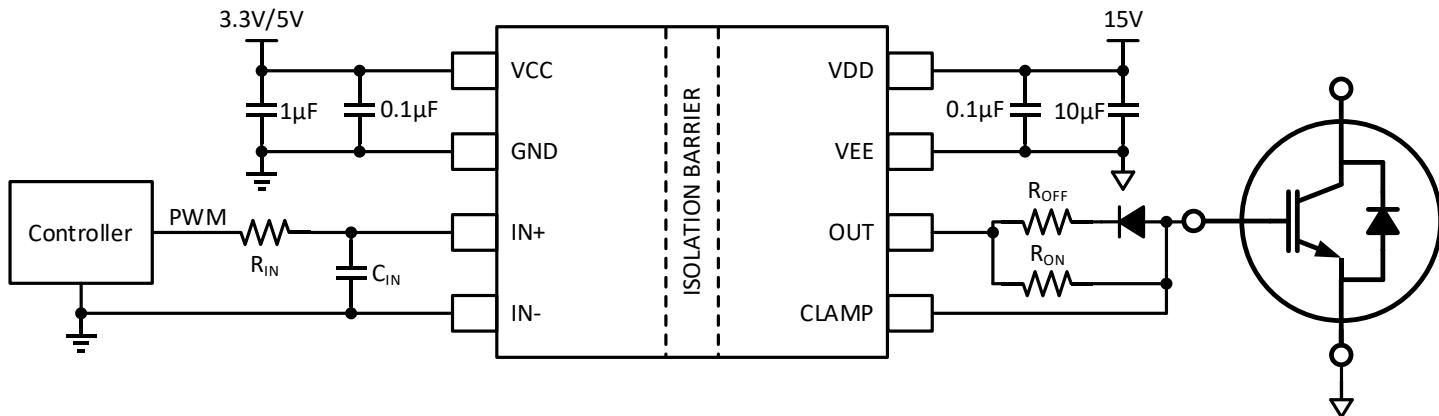

### 9.1. 典型应用

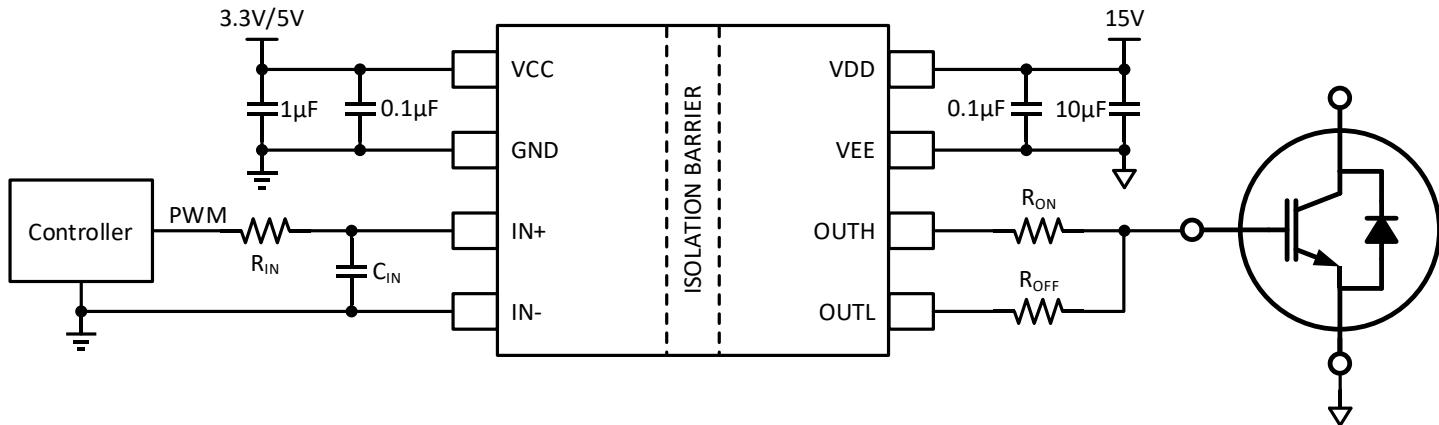

CA-IS3214 具有驱动能力强、隔离等级高、CMTI 优异、主动保护和监测功能优越、高可靠性等特点，在 HEV/EV 中的牵引逆变器、车载充电器、充电桩、电机驱动器、光伏逆变器、储能变流器、充电桩功率模块、工业电源等领域得到广泛应用。CA-IS3214MxxG 的典型应用如图 9-1 所示；CA-IS3214SxG 和 CA-IS3214TSCG 的典型应用如图 9-2 所示。

图 9-1 CA-IS3214MxxG 典型应用

图 9-2 CA-IS3214SxG 和 CA-IS3214TSCG 典型应用

### 9.2. 电源设计

在 OUT 开关瞬间，峰值拉和灌电流由 VDD 和 VEE 电源提供。为了确保电源稳定以及提供 $\pm 10A$  峰值驱动能力，推荐在 VDD 至 COM 和 VEE 至 COM 使用  $10\mu F/50V$  的去耦电容。控制侧的 VCC 至 GND 之间推荐使用  $1\mu F$  的去耦电容。同时，建议每个电源使用额外的  $0.1\mu F$  旁路电容以过滤高频噪声。推荐电容必须选用低 ESR 和 ESL 类型的以避免高频噪声，并且应尽可能靠近 VCC、VDD 和 VEE 引脚，以防止 PCB 布局引起系统寄生耦合噪声。

### 9.3. 输入滤波器

CA-IS3214 在 IN+ 引脚内建  $30ns$  抗尖峰脉冲滤波器，任何小于  $40ns$ （典型值）的信号都可以从输入引脚中被过滤掉。对于嘈杂的电机驱动或牵引逆变器系统，可以在外部添加额外的 RC 低通滤器到输入引脚中，可有效提高噪声免疫力并提高信号完整性。不使用时，IN+、IN- 引脚不应悬空。如果仅使用 IN+ 用于输出配置的同相输入控制，则 IN- 应短接到 GND。低通滤器的目的是过滤掉 PCB 走线寄生产生的高频噪声。在选择低通滤波电阻和电容时，应根据系统要求考虑噪声消隐效果和延迟时间。

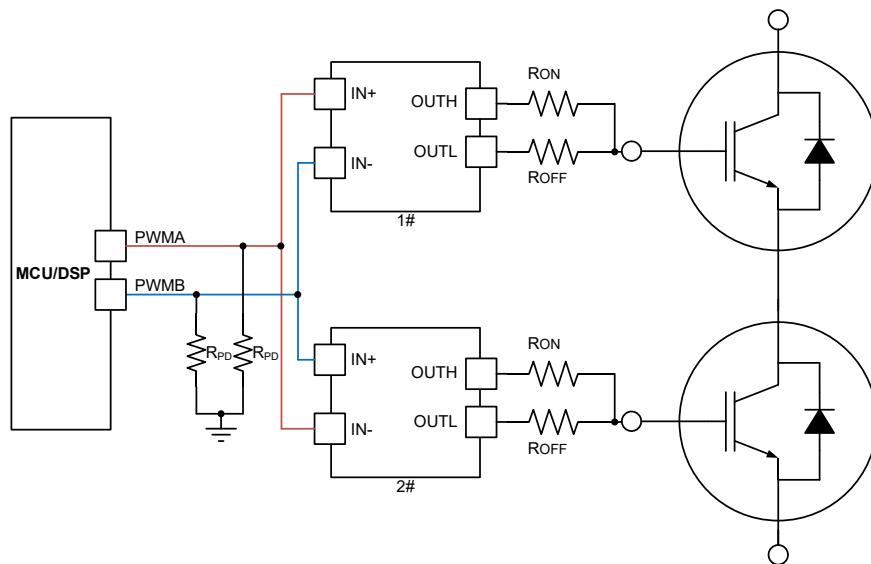

#### 9.4. PWM 内部互锁 IN+和 IN-

CA-IS3214 具有用于 IN+和 IN-引脚的 PWM 内部互锁功能，用于防止同相位桥击穿问题。如图 9-1 所示，以 CA-IS3214Sxx 为例，当 IN+和 IN-均为逻辑高时，驱动输出为逻辑低。若仅使用 IN+，IN-可与 GND 短接。为了利用 PWM 互锁功能，同相位桥中其他开关的 PWM 信号可以发送到 IN-引脚。如图 9-3 所示，PWMA 是到高边开关的 PWM 信号，PWMB 是到低边开关的 PWM 信号。对于高边栅极驱动，PWMA 信号被赋予 IN+引脚，而 PWMB 信号则给予 IN-引脚；对于低边栅极驱动，PWMB 信号被赋予 IN+引脚，而 PWMA 信号则给予 IN-引脚。当 PWMA 和 PWMB 信号都为高时，两个栅极驱动的输出都为低，以防止高边开关和低边开关同时导通。

图 9-3 CA-IS3214Sxx 半桥的 PWM 互锁配置

#### 9.5. 栅极驱动电阻设计

CA-IS3214SxG 和 CA-IS3214TSCG 将输出分离为 OUTH 和 OUTL，从而能够独立控制打开和关闭开关速度。外部栅极驱动电阻对功率管设计尤为关键，当功率管开关时，寄生电感、寄生电容、高  $dv/dt$  和  $di/dt$  以及二极管反向恢复时间都可能导致功率管的不良行为或 EMI 问题。栅极驱动电阻主要对以下三个方面产生影响：驱动电流、开关损耗、上升和下降时间。因此，设计者在实际选取驱动电阻时，需要平衡方案的综合性能参数。峰值拉和灌电流的计算方式如下：

$I_{OUTH}$  峰值拉电流估算公式：

$$I_{OUTH} = \min \left[ 10A, \frac{VDD - VEE}{(R_{OUTH} + R_{GON} + R_{GFETint})} \right]$$

$I_{OUTL}$  峰值灌电流估算公式：

$$I_{OUTL} = \min \left[ 10A, \frac{VDD - VEE}{(R_{OUTL} + R_{GOFF} + R_{GFETint})} \right]$$

其中，

- $R_{OUTH}$  约  $0.5\Omega$ ；

- $R_{GON}$  是外部栅极导通电阻；

- $R_{OUTL}$  约  $0.3\Omega$ ；

- $R_{GOFF}$  是外部栅极关断电阻；

- $R_{GFETint}$  是功率管内部栅极电阻（需查找功率管数据表）。

## 9.6. PCB 设计建议

### 9.6.1. 电源去耦

CA-IS3214 器件在宽电源范围内工作，控制端（VCC）接受 3V 至 5.5V 电源范围，驱动器端最高电压 VDD – VEE 是 33V。使用双极性电源工作时，功率晶体管的栅极相对于发射极/源极的电压为负值时将关闭。这可防止功率晶体管因米勒效应从集电极/漏极感应到栅极的电流而意外开启。这些器件不需要特殊的电源排序。不过，充足的电源旁路和器件接地极为重要。

在外部功率晶体管开启或关闭期间，较高的峰值电流可能会导致 VDD 或 VEE 电压下降。为降低电源纹波并确保栅极驱动器正常工作，VDD 至 VEE 旁路应至少并联一个  $10\mu F$  和  $0.1\mu F$  低 ESR、低 ESL 且额定电压足够的电容。为确保最佳性能，去耦电容应尽可能靠近电源引脚。在控制侧，建议使用  $0.1\mu F$  和  $1\mu F$  并联电容将 VCC 旁路至 GND。

### 9.6.2. PCB 布局指南

由于 CA-IS3214 的驱动能力较强，在 PCB 设计中必须慎重考虑，以下是一些要点：

- 驱动器应尽可能靠近功率器件，以减小 PCB 走线带来的寄生电感。

- 控制侧和驱动侧电源的去耦电容应尽可能靠近电源引脚。每次开关瞬间产生的峰值电流可导致高  $di/dt$  和 PCB 导线寄生电感上的电压峰值。

- 在控制侧使用地线层屏蔽输入信号。输入信号可能因驱动侧开关瞬间产生的高频噪声而失真。地线层为返回电流提供低电感滤波器。

- 如果栅极驱动器用 COM 引脚连接到直流总线负端的低边开关，则使用驱动侧的地线层来屏蔽输出信号免受开关节点产生的噪声的影响；如果栅极驱动器用 COM 引脚连接到开关节点的高边开关，则不建议使用地线层。

- 栅极驱动器下面不允许走 PCB 印制线或覆铜。建议使用 PCB 切口，以避免控制侧和驱动侧之间的任何可能污染增加隔离栅的噪声耦合。

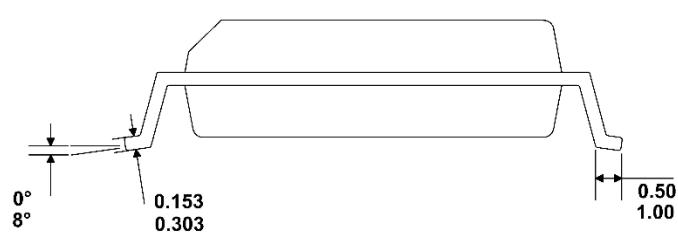

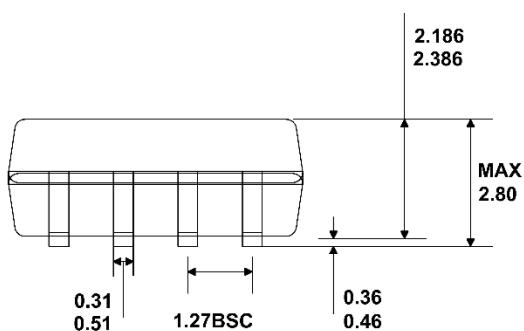

## 10. 封装信息

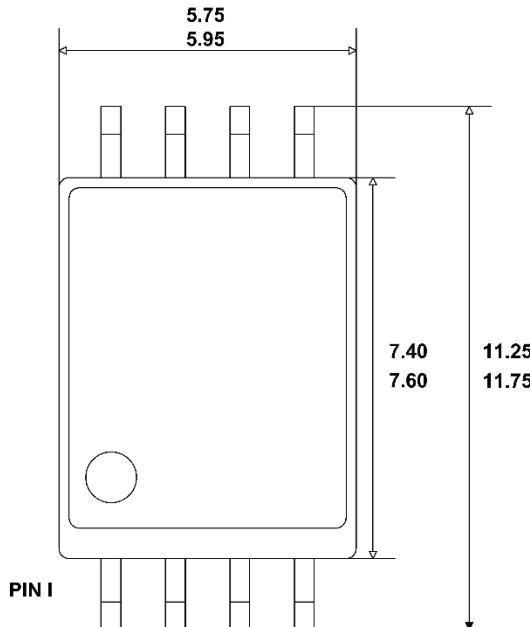

### 10.1. SOIC8-WB 封装尺寸

下图说明了采用 SOIC8-WB 宽体封装的尺寸图和建议焊盘尺寸图，除角度外尺寸以毫米为单位。

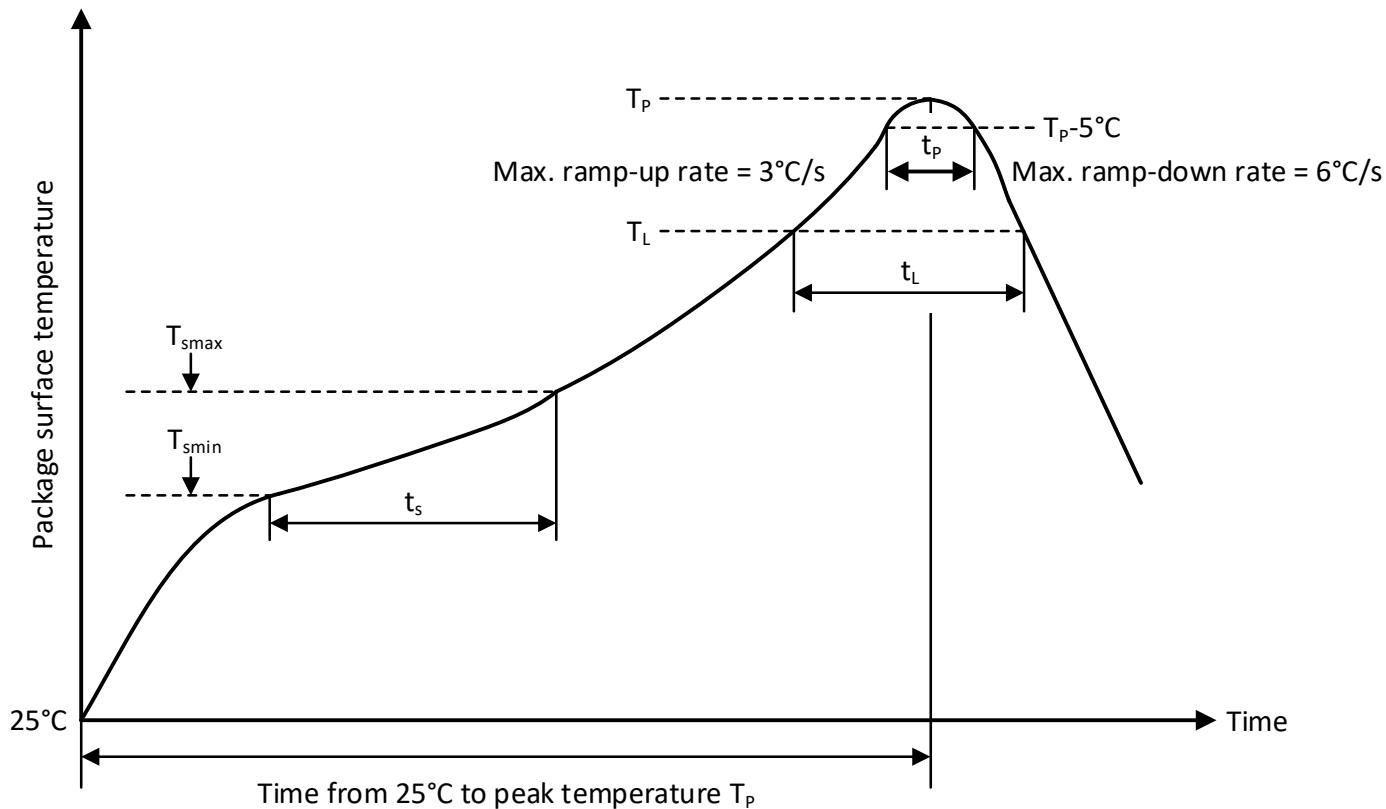

## 11. 焊接信息

图 11-1 焊接温度曲线

表 11-1 焊接温度参数

| 简要说明                                                                         | 无铅焊接                            |

|------------------------------------------------------------------------------|---------------------------------|

| 温升速率 ( $T_L=217^{\circ}\text{C}$ 至峰值 $T_p$ )                                 | 最大 $3^{\circ}\text{C}/\text{s}$ |

| $T_{s\min}=150^{\circ}\text{C}$ 到 $T_{s\max}=200^{\circ}\text{C}$ 预热时间 $t_s$ | 60~120 秒                        |

| 温度保持 $217^{\circ}\text{C}$ 以上时间 $t_L$                                        | 60~150 秒                        |

| 峰值温度 $T_p$                                                                   | $260^{\circ}\text{C}$           |

| 小于峰值温度 $5^{\circ}\text{C}$ 以内时间 $t_p$                                        | 最长 30 秒                         |

| 降温速率 (峰值 $T_p$ 至 $T_L=217^{\circ}\text{C}$ )                                 | 最大 $6^{\circ}\text{C}/\text{s}$ |

| 常温 $25^{\circ}\text{C}$ 到峰值温度 $T_p$ 时间                                       | 最长 8 分钟                         |

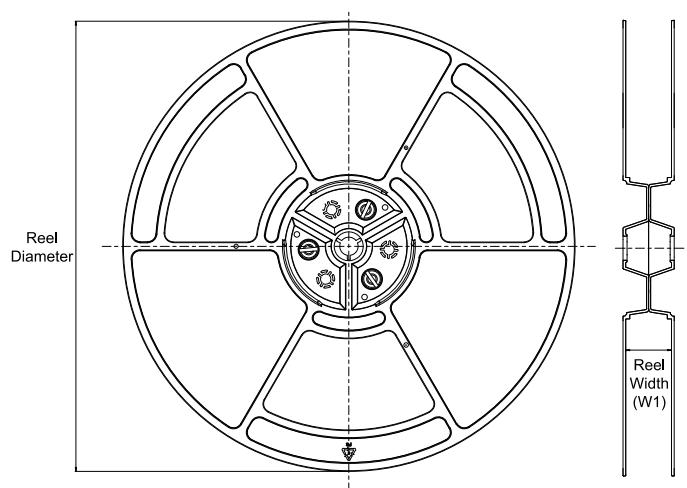

## 12. 编带信息

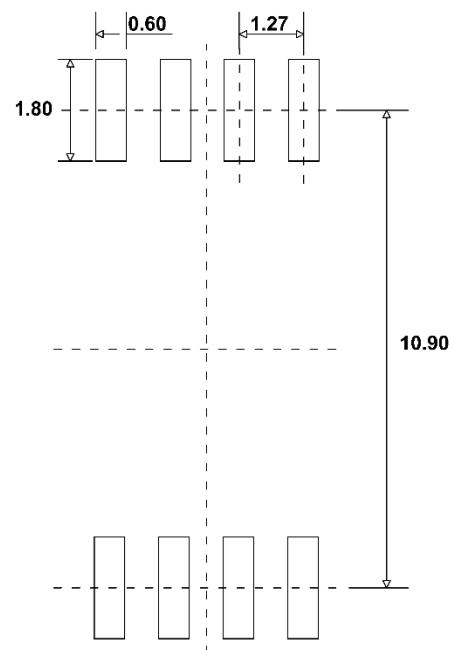

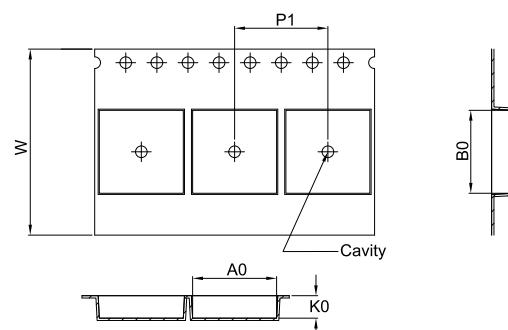

**REEL DIMENSIONS****TAPE DIMENSIONS**

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

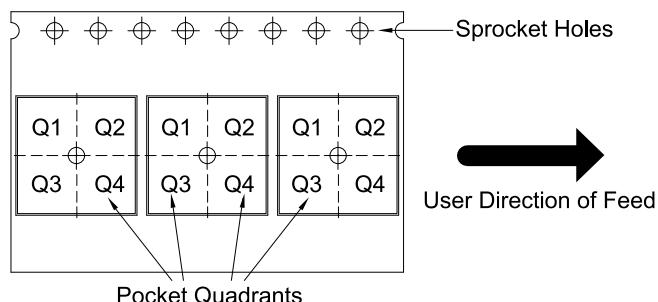

**QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE**

\*All dimensions are nominal

| Device        | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|---------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| CA-IS3214MBG  | SOIC         | G               | 8    | 1000 | 330                | 16.4               | 11.95   | 6.15    | 3.20    | 16.00   | 16.00  | Q1            |

| CA-IS3214MCG  | SOIC         | G               | 8    | 1000 | 330                | 16.4               | 11.95   | 6.15    | 3.20    | 16.00   | 16.00  | Q1            |

| CA-IS3214SBG  | SOIC         | G               | 8    | 1000 | 330                | 16.4               | 11.95   | 6.15    | 3.20    | 16.00   | 16.00  | Q1            |

| CA-IS3214SCG  | SOIC         | G               | 8    | 1000 | 330                | 16.4               | 11.95   | 6.15    | 3.20    | 16.00   | 16.00  | Q1            |

| CA-IS3214TSCG | SOIC         | G               | 8    | 1000 | 330                | 16.4               | 11.95   | 6.15    | 3.20    | 16.00   | 16.00  | Q1            |

### 13. 修订历史

| 修订版本号        | 修订内容 | 修订日期       | 页码 |

|--------------|------|------------|----|

| Version 1.00 | NA   | 2025/11/10 | NA |

#### 14. 重要声明

上述资料仅供参考使用，用于协助 Chipanalog 客户进行设计与研发。Chipanalog 有权在不事先通知的情况下，保留因技术革新而改变上述资料的权利。

Chipanalog 产品全部经过出厂测试。针对具体的应用，客户需负责自行评估，并确定是否适用。Chipanalog 对客户使用所述资源的授权仅限于开发所涉及 Chipanalog 产品的相关应用。除此之外不得复制或展示所述资源，如因使用所述资源而产生任何索赔、赔偿、成本、损失及债务等，Chipanalog 对此概不负责。

#### 商标信息

Chipanalog Inc.®、Chipanalog®为 Chipanalog 的注册商标。

<http://www.chipanalog.com>